# Front-end multi-channel PMT-associated readout chip for hodoscope application

H. Mathez, D. Dauvergne, Y. Zoccarato, Guo-Neng Lu, Shiming Deng

# ▶ To cite this version:

H. Mathez, D. Dauvergne, Y. Zoccarato, Guo-Neng Lu, Shiming Deng. Front-end multi-channel PMT-associated readout chip for hodoscope application. 6th International Conference on New Developments in Photodetection (NDIP 2011), 2011, Lyon, France. pp.390-393, 10.1016/j.nima.2011.11.042. in2p3-00649655

HAL Id: in2p3-00649655 https://hal.in2p3.fr/in2p3-00649655

Submitted on 8 Dec 2011

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Front-end multi-channel PMT-associated readout chip for hodoscope application

Shiming.DENGa,b,\*, Hervé.MATHEZa,b, Denis.DAUVERGNEa, Yannick.ZOCCARATOa,b, Guo-Neng.LUc

#### **Abstract**

For developing a prompt gamma imaging system, we have designed a 16-channel readout chip in a BiCMOS process to be associated with multi-anode photomultipliers (MaPMTs). Each channel has one current input and two separated outputs. The input has very low impedance to minimize electrical crosstalk and effects of capacitances. The two outputs serve to, respectively, detect signal event and quantify signal charge. The channel architecture is a current-mode one, employing a current conveyor to drive both a buffered current comparator and a charge-sensitive amplifier (CSA). The current conveyor is built with super-common-base (SCB) transistor structures to obtain input impedance in the order of a few ohms. Circuit design with the use of bipolar transistor components also improves frequency and noise performances. The chip has been tested and the evaluated characteristics meet the system requirements.

#### Keywords:

prompt gamma imaging system, super-common-base(SCB), current conveyor, charge-sensitive amplifier (CSA),

#### 1. INTRODUCTION

#### References

10

11

22

23

25

27

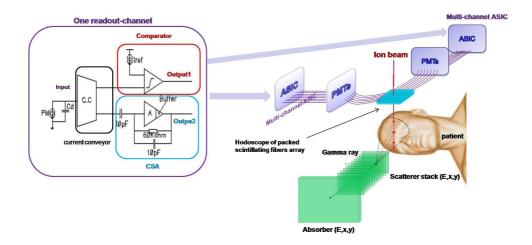

Ion therapy is an innovating technique used to treat tumors with enhanced efficiency for the dose deposition conformation as compared to conventional radiotherapy. It requires real-time control of the dose localization during ion therapy, since slight deviations relative to treatment planning may lead to severe consequences. With the aim of developing a primary beam monitor (a beam hodoscope) for such a quality control [1], we propose a prompt gamma imaging system shown in Figure 1. For typical proton and carbon therapeutic beams, the required hodoscope should have a count rate capability of 10<sup>8</sup> pps, with an accuracy of 1ns. This has led us to implement the system employing arrays of scintillating fibers with read out by MaPMTs or multi-channel plates (MCPs) [2].

The system development requires a dedicated multi-channel readout ASIC (Application Specific Integrated Circuit) to be associated with the MaPMTs. Each channel should have very low input impedance to avoid electrical crosstalk between adjacent channels and to minimize effects of detector and wiring capacitances (Cd + Cw). Crosstalk between channels may degrade position resolution [3], while these capacitances may degrade both frequency and noise performances [3]. Each chanal should also provide two separated outputs corresponding so respectively to high-speed signal-event detection and low-noise signal-charge quantification at low counting rate.

This paper presents a readout chip for this purpose. It has  $_{53}$  been designed in a  $0.35\mu m$  SiGe BiCMOS process (AMS).  $_{54}$

\*Corresponding author

Email address: deng@ipnl.in2p3.fr()

This process allows the use of RF and large-transconductance bipolar components, which is useful for the design of wideband, low-impedance and low-noise circuits with improved performances[3].

#### 2. CIRCUIT DESCRIPTION

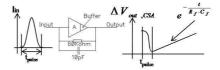

The readout MaPMT-associated chip includes 16 channels whose input impedance should be very low (in the order of ten ohms) to minimize crosstalk and wiring capacitance effects. Each channel is a current-mode architecture (shown in Figure 1) defined to allow better achievements in speed and noise performances. It is composed of a current conveyor (with two current outputs) as an input stage, and two separated output stages: a current comparator as a discriminator for signal-event detection and a charge-sensitive amplifier (CSA) for signal charge quantification. The signal-event detection requires high-speed operations for the current conveyor and the current comparator, while the signal charge quantification has a major low-noise requirement for the current conveyor and the CSA.

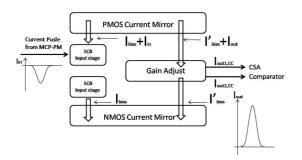

#### 2.1. Current Conveyor

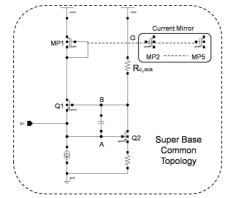

The current conveyor has a low-impedance input and two high-impedance current outputs, with a 4-bit current gain control to compensate effects of optic fiber ageing and the MaPMT's gain dispersion. Figure 2(a) shows the structure of the current conveyor. It employs two Super Common-Base (SCB) transistors [4-5] (see Figure 2(b)) to drive complementary switched current mirrors having variable-gain output branches. The current input signal is applied to one SCB, and a referenced current is applied to the other to cancel bias offset contribution to the output signals.

<sup>&</sup>lt;sup>a</sup>Institut de Physique Nucléaire de Lyon (IPNL), Université de Lyon, Universit Lyon 1, CNRS/IN2P3, F-69622, Villeurbanne, France <sup>b</sup>MICRHAU pôle de MIcroélectronique RHône AUvergne http://micrhau.in2p3.fr

<sup>&</sup>lt;sup>c</sup>Universié de Lyon, Institut des Nanotechnologies de Lyon INL-UMR5270, CNRS, Université Lyon 1, Villeurbanne, F-69622, France

Figure 1: Prompt gamma imaging using a beam hodoscope

Figure 2: (a)Low-impedance, variable-gain current conveyor

Figure 2: (b)super-common-base SCB transistor structure

The SCB transistor shown in Figure 2(b) is basically a common-base topology  $(Q_1)$  with a negative feedback loop <sup>83</sup>  $(Q_2)$ . The input impedance of the current conveyor, mainly determined by that of the SCB, is expressed as:

$$Z_{in} = \frac{1}{(1 + \frac{A_0}{(1 + s/\omega_A)(1 + s/\omega_B)}) \cdot g_{m,Q_1 + sC_A}}$$

$$A_0 = g_{m,Q_2} \cdot R_{C,SCB}$$

<sup>87</sup>

<sup>89</sup>

<sup>90</sup>

$$\omega_A = g_{m,Q_1}/(2\pi \cdot C_A)$$

61

62

$$\omega_{B} = \frac{g_{m,Q_{2}} R_{C,SCB}}{2\pi \cdot (1 + g_{m,Q_{2}} \cdot R_{C,SCB}) \cdot r_{\pi,Q_{1}} \cdot (C_{\pi,Q_{1}} + C_{\mu,Q_{2}})}$$

$$C_{A} = C_{DB,M_{1}} + (1 + g_{m,Q_{2}} \cdot R_{C,SCB}) \cdot (C_{\pi,Q_{1}} + C_{\mu,Q_{2}}) + C_{\pi,Q_{2}} + C_{D}$$

where  $A_0$  is the voltage gain of  $Q_2$  at low frequencies;  $C_A$  is the sum of parasitic capacitances at the input node A (including the detector output capacitance  $C_D$ ),  $\omega_A$  and  $\omega_B$  are poles related respectively to nodes A and B. At moderate frequencies, the input impedance is given by  $Z_A \approx 1/(A_0 \cdot g_{m,Q_1})$ . Thanks to the use of large-transconductance bipolar components in the SCB,  $Z_{in}$  can be reduced to a few ohms.

The current gain of the current conveyor is given by[6]:

$$\frac{I_{out}}{I_{in}} = \frac{g_{m,MP_2 - MP_5}}{g_{m,MP_1}} \times \frac{1}{(1 + \frac{sC_1}{g_{m,Q_1}})(1 + \frac{sC_2}{g_{m,MP_2}})}$$

(2)

with  $C_1 = C_{be,Q_1}$  and  $C_2 = \Sigma C_{nodeG}$ where  $g_{m,MP_2-MP_5}$  is the total transconductance of the 4-bit switched transistors  $MP_2$  to  $MP_5$  in parallel. As  $g_{m,Q_1}(BJT) \gg$  $g_{m,MP_2}(PMOS)$ , and  $C_1 \ll C_2$ , the bandwidth is limited by  $g_{m,MP_2}$  and  $C_2$ .

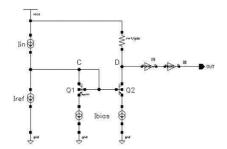

#### 2.2. Current Comparator

The current comparator following the current conveyor detects current signal events. It compares the current conveyor's corresponding output signal (typically lasting a few nanoseconds) with a referenced threshold current and produces a pulsed output voltage response.

Figure 3 shows the current comparator mainly consisting of a signal current mirror and a 2-stage output buffer. The signal current mirror employs bipolar transistor components to reduce its input impedance and to improve the speed performance of the circuit. This current mirror performs current-to-voltage conversion at its output:

Figure 3: Current comparator for signal-event detection

$$\Delta V_D = \begin{cases} \Delta I_c \cdot \frac{g_{m,Q_2}}{g_{m,Q_1}} \cdot \frac{1}{g_{ds} + g_{ce,Q_2}} & when \quad \Delta I_c = I_{in} - I_{ref} > 0\\ 0 & when \quad \Delta I_c = I_{in} - I_{ref} < 0 \end{cases}$$

(3)

The time constants at nodes C and D are respectively  $\tau_C = C_C/g_{m,Q_1}$  and  $\tau_D = C_D/g_{m,Q_2}$  with  $C_C = C_{ce,Q_1} + C_{be,Q_1} + C_{be,Q_2} + (1 + g_{m,Q_2}/g_{ds}) \cdot C_{\mu,Q_2}$  and  $C_D = C_{ce,Q_2} + C_{invertor}$ . As  $C_C \gg C_D$  and  $g_{m,Q_1} < g_{m,Q_2}$ , the speed performance of the current comparator is determined by  $\tau_C$ . It can be optimized by careful layout and proper sizing of transistor components to reduce different capacitance contributions to  $C_C$ . The 2-stage buffer converts  $\Delta$   $V_D$  to a logic-level pulse.

### 2.3. CSA(Charge Sensitive Amplifier)

95

100

102

103

104

105

106

107

108

109

110

111

112

115

116

117

118

119

120

122

123

The CSA consists of a buffered amplifier and a  $R_f C_f$  feed-back network (Figure 4(a)). For a fast input current pulse during ta time  $t_{pulse}(\sim 20ns)$ , the CSA output produces a voltage swing given by:

$$\triangle V_{out,CSA} = -\frac{1}{C_f} \int_0^{t_{pulse}} I_{in}(t)dt \qquad (4)_{12}^{12}$$

After the input current pulse,  $V_{out,CSA}$ , returns exponentially<sub>131</sub> to its steady level with a time constant determined by  $R_fC_{f\cdot_{132}}$ . This time constant is chosen according to the maximum count-<sub>133</sub> ing rate.

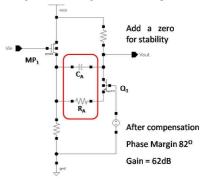

The buffered amplifier has an input part shown in Figure 4(b), which is a folded-cascode structure with  $R_A$  and  $C_A$  for feed-136 forward compensation [7-8]. The second cascode transistor  $Q_{1_{137}}$  is a bipolar component for better gain, speed and/or phase mar-138 gin achievements. The input transistor  $MP_1$  has a large W/L 139 ratio to minimize its noise contribution.

## 3. RESULTS AND DISCUSSION

Figure 5 shows the fabricated readout chip. The chip area including pads is  $6.16mm^2$ . Each channel occupies a surface area of  $680\mu m \times 120\mu m$ . The chip has been tested using a board shown in Figure 6(a).

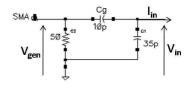

The test board includes a structure shown in Figure 6(b), to generate an input current signal for the testing:

$$I_{in}(t) = \frac{C_g \cdot dV_{gen}(t)}{dt} \tag{5}$$

Figure 4: (a)Charge-Sensitive Amplifier

Figure 4: (b)Amplifiers with feed forward compensation

Figure 5: Microphotograph of the readout chip

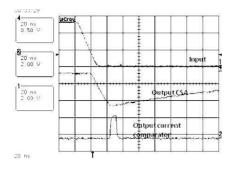

The magnitude of  $I_{in}(t)$  can thus be evaluated from the waveform of  $V_{gen}$ . By measuring directly the magnitude of  $V_{in}$ , the input impedance of the current conveyor can be determined by  $Z_{in} = \frac{\Delta V_{in}}{\Delta I_{in}}$ . We have obtained  $Z_{in} = 12\Omega$ . Figure 7 shows signal waveforms of a channel. The circuit

Figure 7 shows signal waveforms of a channel. The circuit operation is verified by observing the output signal of the current comparator  $V_{out,comp}$  and that of the CSA  $V_{out,CSA}$ : the pulsed output of the current comparator indicates the signal event, and the output signal of the CSA gives a magnitude  $\Delta V_{out,CSA}$ , from which an input signal charge can be evaluated.

For signal-event detection, the detection threshold for the current comparator is set by  $I_{ref}$ , which can be adjusted from  $100\mu A$  to  $400\mu A$ .

For signal charge quantification, the conversion gain at the output of the CSA is 98mV/pC. The evaluated noise in ENC (Equivalent input RMS Noise Charge) is 91fC. The maximum measurable charge before saturation (limited by the current conveyor) is 10 pC. The dynamic range is 36 dB. The crosstalk between adjacent channels is 1.7% (i.e. 35 dB).

Figure 6: (a)Test board

Figure 6: (b)Structure for generating input current signal

141

Figure 7: Signal waveforms of a channel:the two outputs  $V_{out,CSA}$  and  $V_{out,comp169}$  in response to  $V_{gen}$

Table 1: Summary of characteristics of the designed readout ASIC

| Table 1. Summary of characteristics of the designed readout ASTC              |                                                         |                                |

|-------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------|

|                                                                               | Post-Layout results                                     | Test results 17                |

| Power consumption<br>/channel(under 3.3V)<br>@ current gain<br>from 0.25 to 2 | 15 to 22mW                                              | 16 to 23mW <sup>17</sup>       |

| Input dynamic range                                                           | 50µA(525fC)<br>@gain 2<br>—<br>2.4mA(25.2pC)<br>@gain 2 | 177<br>173<br>174<br>184<br>18 |

| Input impedance  @ working frequencies                                        | $4\Omega$                                               | 12Ω 18:                        |

| Current Conveyor<br>Bandwidth                                                 | 200MHz                                                  |                                |

| Current comparator<br>Bandwidth                                               | 667MHz                                                  | 18<br>— 18<br>18               |

| CSA Peaking time                                                              | 30ns                                                    | 28ns 19                        |

| 1-full-channel ENC                                                            | 42fC                                                    | 19fC 19                        |

| Xtalk                                                                         | _                                                       | 1.7%                           |

| Chip Size (including pads)                                                    | 6.61 <i>mm</i> <sup>2</sup>                             | $6.61mm^2$ 19                  |

Table 1 summarizes the measured characteristics of the readout chip in comparison with post-layout simulation results.

We would like to mention that, our readout chip has similar<sup>200</sup> integrated functions to a 10-channel chip reported in [9]. The<sup>201</sup> power consumption and chip sizes are also comparable. We<sup>202</sup> have obtained improved performances especially in terms of  $_{204}$  input impedance (12 $\Omega$  compared to 180 $\Omega$ ), thanks to optimal<sup>205</sup> design with the use of bipolar components in a BiCMOS tech-<sup>206</sup> nology.

#### 4. CONCLUSION

143

145

146

147

149

150

152

153

154

155

156

157

We have designed a 16-channel readout chip in a BiCMOS process to be associated with MaPMTs or MCPs for developing a prompt gamma imaging system. Each channel is a current-mode architecture consisting of three main building blocks: a current conveyor, a buffered current comparator and a CSA. Testing of the chip has shown improved characteristics compared to a reported chip with similar functions. The channel input has very low impedance ( $\sim 12\Omega$ ) to minimize crosstalk

( $\sim 1.7\%$ ). The evaluated speed and noise performances meet the system requirements. We are undertaking a new chip design with performance optimization to reduce power consumption per channel, for high-resolution hodoscopes.

#### 5. ACKNOWLEDGMENT

This work has been carried out in the context of the GAMHADRON project fund by the ANR (Agence Nationale pour la Recherche) and the European project ENVISION. These two projects are devoted to novel imaging systems for in-vivo monitoring and cancer therapy. This work has also been partly supported by the Rhne-Alpes Regional Program for Research in Hadrontherapy.

We would also like to thank Mr. E. Bechetoille and Mr Y. Zoccarato for their technical helps in layout optimization and ASIC design.

#### References

163

164

165

166

- [1] E. Testa, M. Bajard, M. Chevallier, D. Dauvergne, F. Le Foulher, N. Freud, J.M. Létang, J.C. Poizat, C. Ray "Monitoring the Bragg peak location of 73 MeV/u carbon ions by means of prompt -ray measurements", Applied Physics Letters 93, 093506, 2008.4

- [2] P. Achenbach et al "In-beam tests of scintillating fiber detectors at MAMI and at GSI" Nuclear Instruments and Methods in Physics Research A, Volume 593, pp 353-360, 11 August 2008

- [3] F.Anghinolfi, W.Dabrowski, E.Delagnes, J.Kaplon, U,Koetz, P.Jarron, F.Lugiez, C.Posh, S.Roe and P. Weilhammer "SCTA-A Rad-Hard BiCMOS Analogue Readout ASIC for the ATLAS Semiconductor Tracker"

- [4] S. Bondil, K. Borer, A. Cazes, J.E. Campagne, M. Hess, C. De La Taille, A. Lucotte, G.Martin-Chassard, L. Raux, J.P Repellin, "Opera ROC: A frontend chip for opera multi-anode photomultipliers" Nuclear Science Symposium Conference Record, 2003 IEEE, Volume 1, pp 19-25, October 2003.

- [5] S. Callier, F. Dulucq, C. de La Taille, G. Martin-Chassard, N. Seguin-Moreau, R. Gaglione, I. Laktineh, H. Mathez, V. Boudry, J.C Brient, C. Jauffret "HARDROC1, readout chip of the Digital HAdronic CALorimeter of ILC" Nuclear Science Symposium Conference Record; IEEE Volume 1-11, pp 1851 1856 Oct. 26 2007-Nov. 3.

- [6] F.Anghinolfi, P.Aspell, M. Campbell, E.H.M Heijne, P. Jarron, G. Meddeler, J.C Santiard, S. Buytaert "ICON, a current mode preamplifier in CMOS technology for use with high rate particle detectors" Nuclear Science Symposium and Medical Imaging Conference, 1991, Conference Record of the 1991 IEEE, Volume 1, pp 639-633, November 1991.

- [7] H. Mathez et al "A charge-sensitive amplifier associated with APD or PMT for 511 keV, photon-pair detection "Nuclear Instruments and Methods in Physics Research Section A, Volume 613, Issue 1, Pages 134-140, 21 January 2010.

- [8] W. Sansen and Z. Y. Chang, "Feedforward Compensation techniques for High Frequency CMOS amplifier", IEEE J. Solid-State Circ, vol. 25, N6, pp.1590-1595, December 1990.

- [9] N.Ollivier-Henry, J.D.Berst, C.Colledani, Ch.Hu-Guo, N.A.Mbow, D.Staub, J.L Guyonnet, Y.Hu "A front-end readout mixed chip for high efficiency small animal PET imaging", Nuclear Instruments and Methods in Physics Research A 571 (2007) 312-316

209

210